### **Cell Processor and Playstation 3**

Guillem Borrell i Nogueras

February 24, 2009

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ─ □ ─ の < @

- Cell systems

- Bad news

- More bad news

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ─ □ ─ の < @

- Good news

- Q&A

# **IBM Blades**

< □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □

#### QS21

- Cell BE based.

- 460 Gflops Float

- 20 GFLops Double

- QS22

- PowerXCell 8i based

- 460 GFlops Float

- 200 GFlops Double

# **IBM Blades**

◆□▶ ◆□▶ ▲□▶ ▲□▶ □ のQ@

#### QS21

- Cell BE based.

- 460 Gflops Float

- 20 GFLops Double

- QS22

- PowerXCell 8i based

- 460 GFlops Float

- 200 GFlops Double

- No SPU Double precision improvements expected from IBM

# **Playstation 3**

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ─ □ ─ の < @

- Cell BE based.

- 460 Gflops Float

- 20 GFLops Double

# **Playstation 3**

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ - 三 - のへぐ

- Cell BE based.

- 460 Gflops Float

- 20 GFLops Double

- 256 MB RAM

#### **IBM Power 7**

▲□▶ ▲□▶ ▲□▶ ▲□▶ = 三 のへで

- 8 cores

- 4 threads per core (32 Threads!)

- ? SPE

#### **IBM Power 7**

▲□▶ ▲□▶ ▲□▶ ▲□▶ = 三 のへで

- 8 cores

- 4 threads per core (32 Threads!)

- ? SPE

- 1 TFlop on a chip

### **Cell Broadband Engine**

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ ─臣 ─のへで

# ¿How does it compute?

◆□▶ ◆□▶ ▲□▶ ▲□▶ ■ ののの

- PPU starts a program

- PPU loads an SPU context on a thread

- SPU context loads all necessary data into its LS

- SPU executes context

- SPU ends the task and returns control to PPU

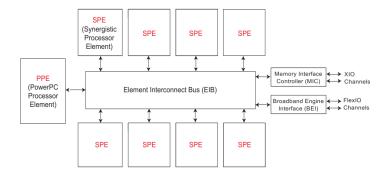

| Synergistic Processor Element (SPE) |

|-------------------------------------|

| Synergistic Processor Unit (SPU)    |

| Local Store (LS)                    |

| Memory Flow Controller (MFC)        |

| DMA Controller                      |

|                                     |

#### PPE PowerPC Processor Element

- PPU PowerPC Processor Unit

- **EIB** Element Interconnect Bus

- SPE Synergistic Processor Element

- SPU Synergistic Processor Unit

- MFC Memory Flow Controller

- DMA Direct Memory Access

- SIMD Single Instruction Multiple Data

(ロ) (同) (三) (三) (三) (三) (○) (○)

# Dumb vector unit

▲□▶ ▲□▶ ▲□▶ ▲□▶ = 三 のへで

- General purpose vector unit

- Designed to run code

- Altivec unit on a box

- IBM called that VMX

# Dumb vector unit

< □ > < 同 > < Ξ > < Ξ > < Ξ > < Ξ < </p>

- General purpose vector unit

- Designed to run code

- Altivec unit on a box

- IBM called that VMX

- LS is regiser based

- No type distinction

- Data should be aligned by hand

# Dumb vector unit

◆□▶ ◆□▶ ▲□▶ ▲□▶ ■ ののの

- General purpose vector unit

- Designed to run code

- Altivec unit on a box

- IBM called that VMX

- LS is regiser based

- No type distinction

- Data should be aligned by hand

- MFC is a DMA controller

- Data moved with DMA primitives.

- No data scheduling

- No data implicit copying.

# SIMD Programming

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ - 三 - のへぐ

- SPUs are programmed using SIMD primitives

- Like a vector unit

# SIMD Programming

< □ > < 同 > < Ξ > < Ξ > < Ξ > < Ξ < </p>

- SPUs are programmed using SIMD primitives

- Like a vector unit

- Almost coding in assembly

- Access assembly instructions via libspu2

- Add to that DMA instructions

# SIMD Programming

◆□▶ ◆□▶ ▲□▶ ▲□▶ ■ ののの

- SPUs are programmed using SIMD primitives

- Like a vector unit

- Almost coding in assembly

- Access assembly instructions via libspu2

- Add to that DMA instructions

- That can take us ages

# PPU and SPU code

▲□▶ ▲□▶ ▲□▶ ▲□▶ = 三 のへで

- PPE have L1 and L2 cache.

- SPE have LS (register based)

# PPU and SPU code

◆□▶ ◆□▶ ▲□▶ ▲□▶ ■ ののの

- PPE have L1 and L2 cache.

- SPE have LS (register based)

- Their ssembly has nothing to do

- They are compiled separately.

- PPU code cannot be reused.

# PPU code libraries

< □ > < 同 > < Ξ > < Ξ > < Ξ > < Ξ < </p>

- BLAS (Basic Linear Algebra Subroutines)

- LAPACK (Linear Algebra Package)

- FFTW (The Fastest Fourier Transform in the West)

- C and Fortran interfaces

- Fortran interface is not complete

# PPU code libraries

(日) (日) (日) (日) (日) (日) (日)

- BLAS (Basic Linear Algebra Subroutines)

- LAPACK (Linear Algebra Package)

- FFTW (The Fastest Fourier Transform in the West)

- C and Fortran interfaces

- Fortran interface is not complete

- Almost all we need is in Cell SDK!

# Thin ice

< □ > < 同 > < Ξ > < Ξ > < Ξ > < Ξ < </p>

- PPU code means no SPU control.

- Data must be aligned too using posix\_memalign.

- If SPU control is needed PPU code cannot be used at all

- Tells us what we can or cannot do

- BSC has been using those for about 2 years.

# Optimizing compilers

◆□▶ ◆□▶ ▲□▶ ▲□▶ □ のQ@

- Cell Superscalar

- Alpha state

- OpenMP-like annotations

- BSC

- Free Software

- XL compilers for Multicore Acceleration

- Alpha state

- OpenMP support

- MASS (Mathematical Acceleration Subsystem)

- Worth the money

#### Conclusions

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ● □ ● ● ● ●

• PPU code is possible

# Conclusions

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ - 三 - のへぐ

- PPU code is possible

- SPU code is not possible for us

- 2 options:

- Cell SDK for Multicode Acceleration

- Optimizing Compiler (WAIT)

# Conclusions

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ - 三 - のへぐ

- PPU code is possible

- SPU code is not possible for us

- 2 options:

- Cell SDK for Multicode Acceleration

- Optimizing Compiler (WAIT)

- Get a good C book.

# Q&A

◆□ > ◆□ > ◆ 三 > ◆ 三 > ● ○ ○ ○ ○